The market for low-power microcontrollers (MCUs) used in IoT endpoint devices is fiercely competitive and not for the weak of heart. If you are a purveyor of such a low-power MCU, you have to have something really special to differentiate yourself and stand proud in the crowd. All of which leads us to…

…those clever chaps and chapesses at Ambiq. If you are already familiar with Ambiq, you’ll be interested to hear about their latest and greatest offerings. Alternatively, if the Ambiq moniker has never tickled your ears or tempted your eyes, then HIGNFY (have I got news for you)? (That’s a rhetorical question because I do indeed have news for you.)

Recently, I was chatting with Dan Cermak, who is VP of Architecture and Product Planning at Ambiq. I remember when this company was just starting out, deep in the mists of time that we used to call 2010. You never know how these things are going to turn out, so I was delighted to hear that they are currently shipping 1 million devices a week. This may not sound like much to the Intels and Microchips of this world, but it’s pretty darned impressive for a small company in an intensely competitive field.

The foundation upon which Ambiq’s success is built is the company’s patented subthreshold power optimization technology, or SPOT for short. You have to remember that I hail from the days of the Texas Instruments (TI) SN7400-series transistor-transistor logic (TTL) devices, whose outputs switched between 0V and 5V, which is exactly the way the creator of the universe intended things to be. When the first microprocessor units (MPUs) arrived on the scene, both their cores and their general-purpose input/outputs (GPIOs) ran at 5V.

Later, this was reduced to 3.5V or 3.3V. Personally, I find MPUs and MCUs whose GPIOs switch between 0V and 3.3V to be a tad disconcerting. The next advance was to maintain the GPIOs at 3.3V (or whatever signaling standard is used by the device in question), but to reduce the voltage of the core logic where all of the number crunching and decision making takes place.

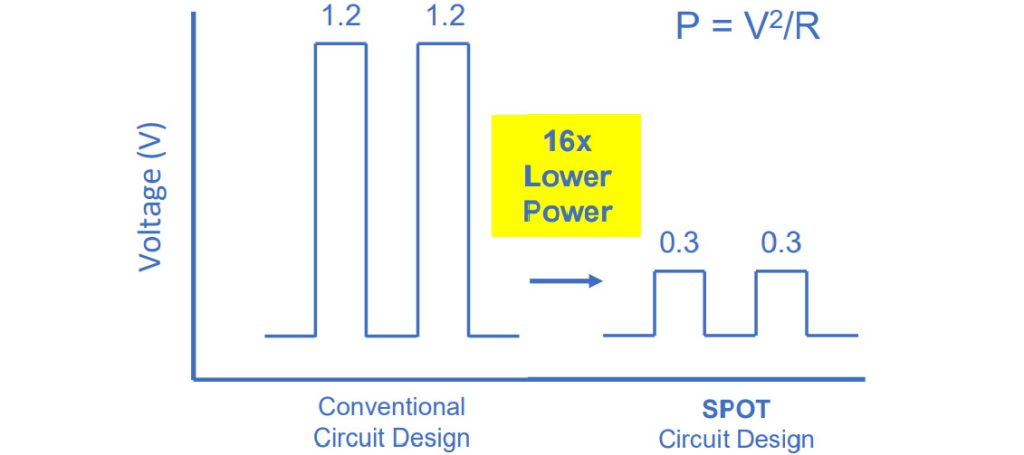

In fact, the core voltages in many devices have been falling for years, starting at 2.9V and wending their way ever lower, with some extreme cases falling as low as 0.9V or 0.8V, although 1.2V is as low as many players are prepared to go.

And then we have Ambiq, whose processors are based on their SPOT, with a core voltage of only 0.3V (this nugget of knowledge alone would have blown my socks off had I not donned special elasticated versions for the purposes of writing this column).

Can you spot the difference? (I’m sorry; I couldn’t help myself)

(Image source: Ambiq)

Since the folks at Ambiq are the proud possessors of more than 50 blocking patents, they are sitting in the catbird seat, as it were. Furthermore, since the amount of dynamic (switching) power consumed in a silicon chip is a square of the voltage, this means that an MPU or MCU core implemented using the SPOT architecture has a dynamic power consumption 16X lower than an equivalent core running at 1.2V. That’s a substantial differentiator, whichever side you butter your toast.

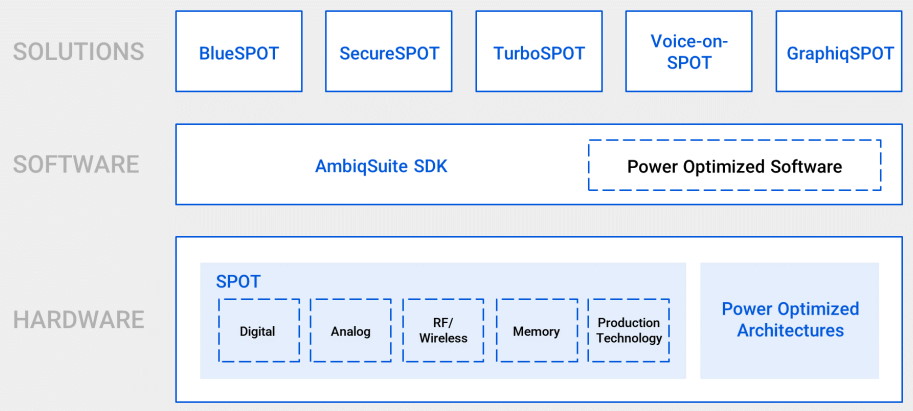

Since I’m into technology, this is the way I think about SPOT. In reality, however, SPOT is also a platform for designing ultra-low-power System-on-Chip (SoC) devices.

SPOT is a platform for SoC design (Image source: Ambiq)

At the bottom of the pile, conceptually speaking, we have power-optimized SPOT architectures for analog, digital, RF/wireless, memory, etc. (the “etc” means I don’t know to what the “production technology” item in this illustration refers and I haven’t got the strength to find out).

Sitting on top of the hardware, we have the first layer of software in the form of the AmbiqSuite software development kit (SDK). This includes a hardware abstraction layer (HAL), device drivers, and example applications to speed the understanding of the operation of Ambiq’s MCUs. (Third party software including the ARM/PacketCraft Cordio BLE Host stack and FreeRTOS v10.1.1 are distributed along with debugging tools and other support.)

In addition to user-defined applications, the folks at Ambiq also provide a bunch of solutions. For example, BlueSPOT is Ambiq’s ultra-low power Bluetooth Low Energy (BLE) technology. SecureSPOT enables robust security features such as secure boot, secure key management, secure over-the-air (OTA) patches and updates, anti-rollback, etc. TurboSPOT is Ambiq’s ultra-low power dynamic performance scaling technology, which enables a higher frequency operating mode for the CPU and memory. And Voice-on-SPOT (VOS), is a complete, always-on, always-listening, voice-to-cloud solution for local voice commands and/or voice assistant integration in battery-powered IoT endpoint devices.

The first members of the fourth generation of Ambiq’s Apollo MCU family were introduced in 2020. Based on a high-performance 32-bit Arm-Cortex M4F core implemented in Ambiq’s SPOT, the Apollo4 runs up to 192 MHz with dynamic power consumption as low as 4µA/MHz, which can dramatically extend the battery life of mobile and wearable devices.

The Apollo4 family provides an end-to-end audio subsystem, optimizes graphics functions for wearables with rich displays, offers flexible peripherals (for sensors, GPS location services, and more), features robust, built-in security features and hardware crypto accelerators, and… the list goes on.

A couple of weeks ago as I pen these words, Ambiq introduced the latest addition to the Apollo4 family — the Apollo4 Plus — which provides enhanced graphics display and greater voice capabilities to serve as either an application processor (AP) or a coprocessor for battery-powered endpoint devices. The Apollo4 Plus is now in mass production, targeting smartwatches and smart bands, consumer medical devices, motion and tracking units, and the smart home of the 21st century.

But wait, there’s more, because Ambiq has also announced the Apollo4 Blue Plus, which augments the features and functions of the Apollo4 Plus with embedded BLE 5.1 for Bluetooth connectivity to smartphones or other devices.

On their website, the Ambiq guys and gals say that they are “committed to further improve the quality of life by enabling the intelligence of endpoints while further reducing carbon footprints.” This is an awesome goal to strive for, and it’s something they can actually achieve with the latest and greatest members of the Apollo4 family. What say you? Are you as interested in learning the ins-and-outs and the nitty-gritty details of Ambiq’s subthreshold technology as am I?

You must be logged in to post a comment.

Sponsored by Cadence Design Systems

Optimize your verification workload, boost coverage, and accelerate root cause analysis to reduce silicon bugs and accelerate your time to market with Cadence Verisium AI-Driven Verification. Learn how this generational shift from single-run, single-engine algorithms to algorithms leverages big data and AI across multiple runs of multiple engines throughout an entire SoC verification campaign.

Click here for more information

Sponsored by Texas Instruments

TI’s SHP space-qualification level provides higher thermal efficiency, a smaller footprint and increased bandwidth compared to traditional ceramic packaging. The common package and pinout between the industrial- and space-grade versions enable you to get the newest technologies into your space hardware designs as soon as the commercial-grade device is sampling, because all prototyping work on the commercial product translates directly to a drop-in space-qualified SHP product.

Click to read more

Sponsored by Infineon

Today’s AI and Networking applications are driving an exponential increase in compute power. When it comes to scaling power for these kinds of applications with next generation chipsets, we need to keep in mind package size constraints, dynamic current balancing, and output capacitance. In this episode of Chalk Talk, Mark Rodrigues from Infineon joins Amelia Dalton to discuss the system design challenges with increasing power density for next generation chipsets, the benefits that phase paralleling brings to the table, and why Infineon’s best in class transient performance with XDP architecture and Trans Inductor Voltage Regulator can help power your next high performance ASIC, SoC or xPU design.

Click here for more information about computing and data storage from Infineon